满足 5G 及未来技术需求

5G 的兴起正在彻底改变电信和网络行业的格局。在以下这些重要发展趋势的大背景下,提供商必须能够高效应对不断增长的海量数据以为客户带来更丰富的体验和服务(从 VR/AR 到对延迟敏感的物联网应用等)。

指数级数据增长

随着需要通过网络发送的数据量大幅增加,网络技术也需要进行相应的重大改进。

解聚

向软件定义、云原生、解聚化和容器化环境发展的趋势推动了敏捷交付和效率提升。

分布式计算

为了实现 5G 所需的低延迟,计算正在从核心向边缘扩展。

能效需求

由于电信运营商面临日益严峻的碳减排压力,寻找更高能效的解决方案变得越来越重要。

应用场景

- 访问

- 电信边缘计算

- 分组核心

- 城域和传输网络

- 数据中心

接入网络

无线/无线电

AMD Zynq™ UltraScale+™ RFSoC 有助于降低功耗、提高可扩展性,并轻松适应各种新标准。针对波束成形/MIMO,AMD Versal™ AI Core 自适应 SoC 可提供系统级计算能力,能够即时计算每个无线电单元所需的相位和增益系数。

分布式单元

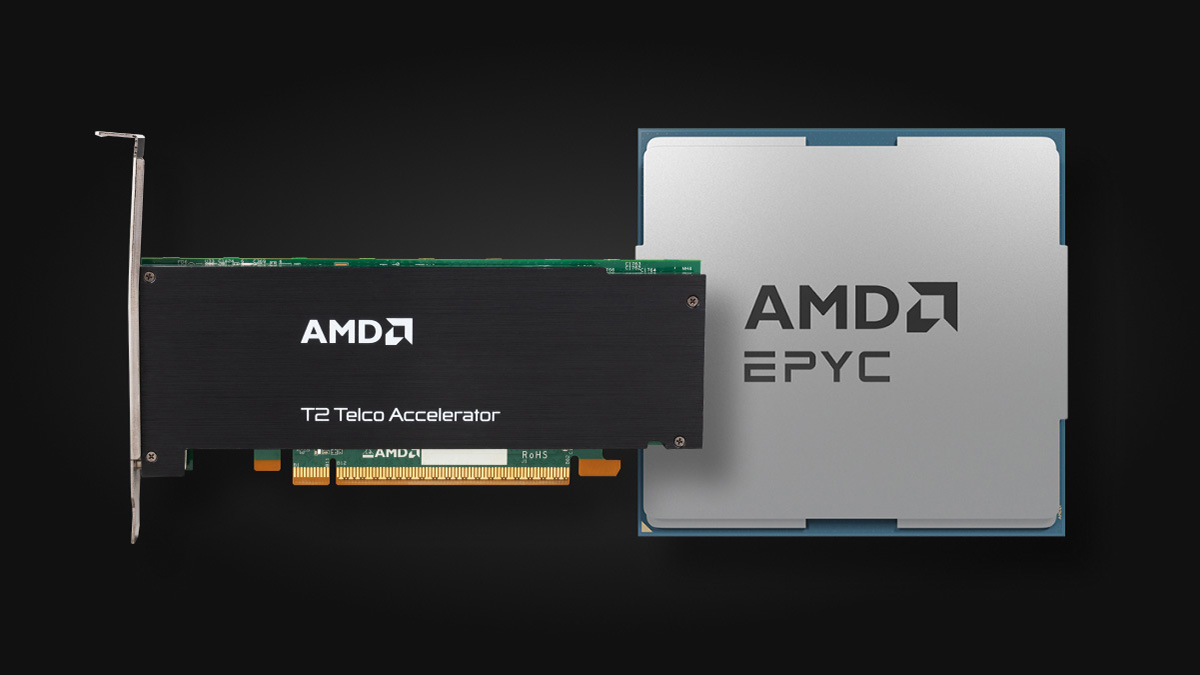

分布式单元通常对功耗和尺寸有严格限制。AMD EPYC(霄龙)8004 系列处理器拥有出色的核心密度和性能,并且能够以不高于 200W 的较低功耗正常运行。该系列处理器可与 AMD T2 加速器卡配合使用,帮助减轻延迟敏感型和吞吐量密集型 5G 基带功能的负载。

有线/宽带

AMD Zynq UltraScale+ RFSoC 以创新方式整合网络功能和模拟前端,可在聚合接口网络和 DOCSIS 3.1/4.0 之间进行桥接。

聚合接入

AMD 解决方案可以实现与多个不同的无线电单元或其它端点通信,通过任意网络进行传输,然后远程重新生成每个通道。通过整合为可重配置的统一 AMD 解决方案,不仅可以降低前期系统成本,而且还能够使用低成本的可扩展分组网络。无论是针对 O-RAN (eCPRI)、PON,还是各种以太网标准,AMD 收发器技术均可带来内置的灵活性和卓越性能,可有效应对各种端口/协议的 X-haul 网络。可重配置的逻辑支持根据所需的传输产品提供定制解决方案。AMD Versal Premium 自适应 SoC 支持从 1GE 到 112Gb/s 的速率,便于选择传输介质,无论是单相干光纤,还是现有网络,均可使用。

网络安全性

自适应 SoC 和 FPGA 安全性

在安全性方面,现代环境带来了双重挑战。首先,数据传输的速度和馈送规模都有大幅增长,因此安全要求更高。除此之外,为了应对新的威胁,出现了越来越多的标准和越来越复杂的算法。

在 AMD 可编程逻辑中,多项安全性功能可以直接实现,并可随着各项标准的发展和新威胁的出现而轻松迭代。AMD 安全性解决方案涵盖从 100M 到 400G 的线速率、加密协议、各种数据包处理和查找等方面,甚至包括基于机器学习算法的预测性恶意软件检测。这些解决方案不仅可确保系统当下安全无虞,更可满足未来需求。

服务器处理器安全性

AMD EPYC(霄龙)处理器内置 AMD Infinity Guard1,这是一套完整的安全功能,有助于确保数据安全无虞。

它包括有助于保护虚拟机隐私和完整性的安全加密虚拟化 (SEV)、具有强大内存完整性保护功能的安全嵌套分页 (SEV-SNP)、有助于抵御对主内存的攻击的安全内存加密 (SME),以及具有硬件强制堆栈保护功能、可抵御恶意软件攻击的 AMD Shadow Stack™。

成功案例

资源

立即联系

联系 AMD 销售代表。

附注

- GD-183:AMD Infinity Guard 的功能随 EPYC(霄龙)处理器的更新迭代而有所变化。Infinity Guard 的安全功能必须由服务器 OEM 和/或云服务提供商启用才能使用。请联系您的 OEM 厂商或提供商,以确认是否支持这些功能。有关 Infinity Guard 的更多信息,请访问 https://www.amd.com/zh-cn/products/processors/server/epyc/infinity-guard.html