Vitis 软件平台开发环境

AMD Vitis™ 软件平台是一款开发环境,主要用于开发包括 FPGA 架构、Arm® 处理器子系统和 AI 引擎在内的设计。Vitis 工具可与 AMD Vivado™ Design Suite 结合使用,为设计开发提供更高层次的抽象。

Vitis 软件平台包含以下工具:

- Vitis Embedded - 用于开发在嵌入式 Arm 处理器上运行的 C/C++ 应用代码

- 编译器和仿真器 - 用于使用 AI 引擎阵列实现设计

- Vitis HLS - 用于开发基于 C/C++ 的 IP 块,该 IP 块主要针对 FPGA 架构

- Vitis Model Composer 是一种基于模型的设计工具,可在 MathWorks Simulink® 环境中进行快速设计探索。

- 一系列性能优化的开源库函数,如 DSP、视觉、求解器、超声和 BLAS 等,其可采用 FPGA 架构实现,也可使用 AI 引擎实现

工具与库

Vitis 嵌入式

Vitis™ Embedded 是一个独立的嵌入式软件开发包,用于开发在嵌入式 Arm 处理器上运行的主机应用。

Vitis AIE DSP 设计工具

编译器和仿真器

AMD Versal™ 自适应 SoC 器件采用 AI 引擎阵列,可在经过资源和功耗优化的情况下实现高性能 DSP 功能。 通过将 AI 引擎与 FPGA 结构资源结合使用,能够非常高效地实现高性能 DSP 应用。

Vitis HLS

Vitis HLS 工具允许用户将 C/C++ 函数综合至 RTL,从而轻松创建复杂的 FPGA 算法。

Vitis HLS 工具与 Vivado™ Design Suite(用于综合、布局和布线)及 Vitis 统一软件平台(用于异构系统设计和应用)紧密集成。

Vitis Model Composer

Vitis Model Composer 是一款基于模型的设计工具,可在 MathWorks Simulink® 环境中实现快速的设计探索。

此外,该工具还允许您使用一系列 AI 引擎和可编程逻辑 (HDL/HLS) 块对设计进行建模和仿真。

Vitis 库

性能优化的开源库,提供开箱即用的加速,对于采用 C、C++ 编写的现有应用而言,代码修改极少,甚至不需要修改代码。

按原样利用特定领域的加速库,通过修改适应您的需求,或者在您的自定义加速器中用作算法构建块。

工具使用

必须使用不同的 Vitis 工具来构建 AMD 自适应 SoC 和 FPGA 的不同部分。

| FPGA(可编程逻辑) | 处理子系统 | AI 引擎 |

|---|---|---|

| Vivado Design Suite/Vitis HLS/Vitis Model Composer | Vitis 嵌入式 | AIE 编译器和仿真器/Vitis Model Composer |

设计流程

Vitis 嵌入式软件开发流程

(以前称为嵌入式 SDK,主要针对早期的 FPGA 系列)

从 Vivado 导出硬件,作为平台文件 |

开发应用代码

|

调试并生成引导映像 |

在 AMD 自适应 SoC 中为 Arm® 嵌入式处理器子系统开发 C/C++ 代码的设计人员通常会使用该流程。

- 通过使用 AMD Vivado™ Design Suite,硬件工程师不仅可以设计可编程逻辑,还可将硬件导出为 Xilinx Support Archive (XSA) 文件。

- 软件工程师可将这些硬件设计信息整合到他们的目标平台中,并可使用 Vitis 嵌入式软件开发应用代码。

开发人员可在 Vitis 嵌入式软件中执行所有系统级验证,并通过生成启动镜像来启动应用。

如需详细了解使用 Vitis 软件平台开发嵌入式软件应用的工作流程,请参阅用户指南 (UG1400) 中的“使用 Vitis 工具开发嵌入式软件”部分。

Vitis 系统设计流程

(硬件与软件)

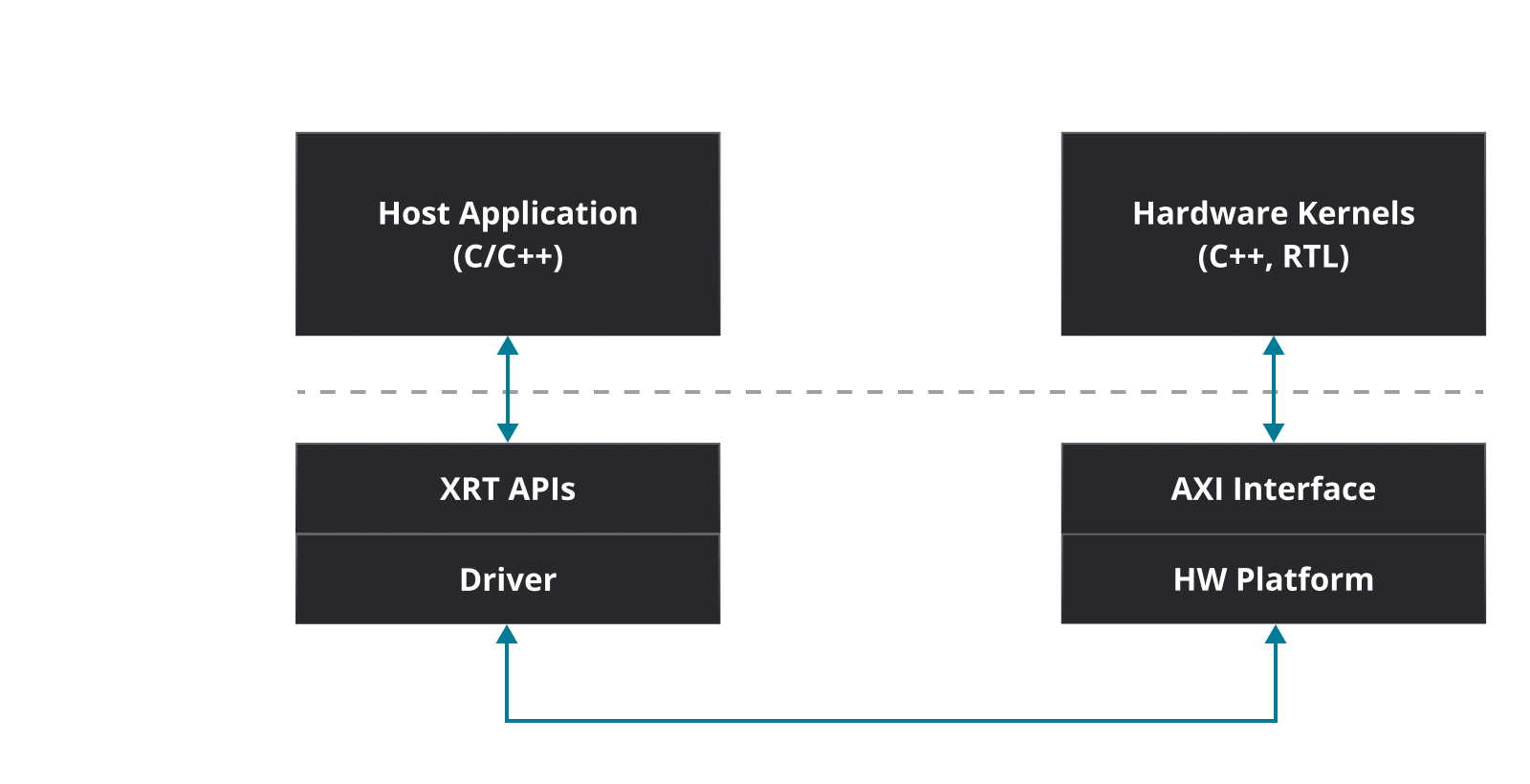

在 AMD 自适应 SoC 中集成其设计软硬件部分的系统设计人员通常会使用该流程。

该流程用于开发异构嵌入式系统设计,其中包括运行在 Arm® 嵌入式处理器上的软件应用,以及运行在可编程逻辑 (PL) 和 / 或 Versal™ AI 引擎阵列上的计算内核等。

该流程包括:

- 采用 C/C++ 编写的软件主机应用,通常运行在嵌入式 Arm 处理器子系统上。使用通过 AMD Vitis 运行时库实现的本机 API 与 AMD 器件内的硬件内核进行交互。

- 硬件内核可使用 AMD Vitis™ HLS 工具从 C++ 生成,也可使用 AMD Vivado™ Design Suite 直接在 RTL 中描述。

如需详细了解使用 Vitis 统一软件平台时的异构系统设计流程,请参阅用户指南 (UG1393) 中的“使用 Vitis 工具进行异构系统设计”部分。

AMD Alveo™ 数据中心加速卡采用相同的系统设计流程:软件程序运行在 x86 主机上,内核运行在 PCIe® 连接的加速卡上的 FPGA 中。如需详细了解使用 Vitis 统一软件平台实现数据中心加速的流程,请参阅用户指南 (UG1393) 中的“使用 Vitis 工具实现数据中心加速”部分。

2024.2 版新增功能

AMD Versal™ AI 引擎 DSP 设计优化

- 使用 Vitis 分析器进行延迟和吞吐量估算

- 使用 Vitis 分析器标记不可用的 PLIO

- 报告堆栈和程序内存使用情况

- 使用全新流程快速实现 Versal AI Engine 设计的原型开发

适用于 AI 引擎的全新增强型 Vitis 库函数

- 适用于 Versal AI Core 系列(含 AIE)的增强型 DSP 库函数:TDM FIR 滤波、更高性能的 GEMM/GEMV、2D IFFT

- 适用于 Versal AI Edge 系列(含 AIE-ML)的全新 DSP 库函数:TDM FIR 滤波、对 Radix-3/Radix-5 FFT 的支持、GEMM/GEMV

AMD Vitis IDE 的重大改进(全新图形用户界面)

- 全新串口终端:监控来自硬件的串口消息

- 扩展程序商城 – 安装并查看第三方扩展程序

- PS 跟踪 – 用于调试和优化嵌入式系统性能的新功能

如需了解更多详情,请访问“新增功能”页面和 AMD Vitis IDE 页面。