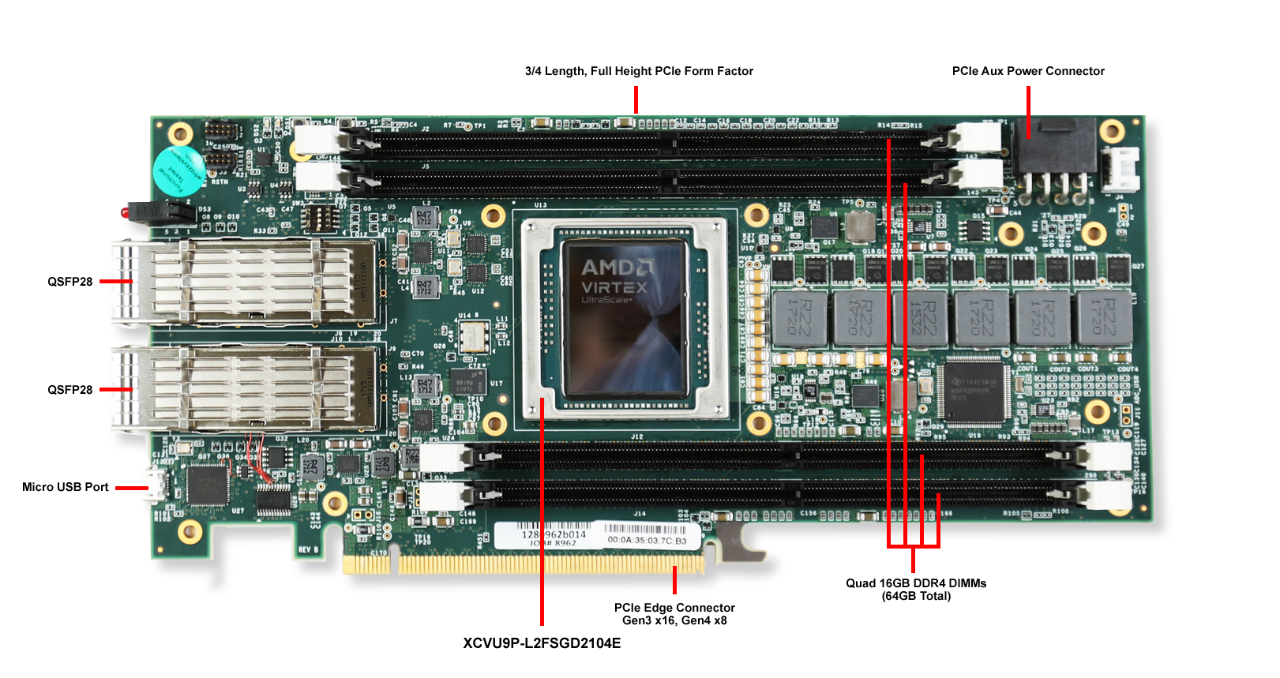

AMD Virtex UltraScale+ FPGA VCU1525 加速开发套件(无源)

Virtex UltraScale+ FPGA 加速开发套件是超大规模应用开发者的完美入门套件。

概述

重要提示:

该开发套件已停产(根据 PDN 咨询 XCN18025),并不再出售。 针对该产品的解决方案将不再进行更新,AMD 将提供有限支持。

产品描述

适合想要充分利用 Virtex™ UltraScale+™ FPGA 高级功能的数据中心应用开发者。这款 PCIe® 开发板可在云端访问,也可通过框架、库、驱动程序和开发工具进行本地访问,从而可通过 AMD SDAccel™ 开发环境使用 OpenCL™、C、C++ 和 RTL 轻松进行应用编程。

主要性能和优势

- 可重编程的专用硬件适应于计算密集型应用,专门针对实况视频转码、数据分析、基因组学以及机器学习的快速增长市场

- 符合双插槽 PCIe 3/4 长全高外形标准

- 可采用支持达 225W 的电路板通过服务器 CPU 实现 10 至 100 倍的性能加速

- 面向定制开发板支持的 SDAccel 平台参考设计

- 采用 SDAccel 开发环境,支持 OpenCL、C、C++ 和 RTL

- VU9P Virtex UltraScale+ FPGA

- 21 TOPs(8 位整数精度)

- 346Mb 的片上内存

- 64GB 的板载 DDR4 DIMM 内存

特色 AMD 器件

包含 XCVU9P-L2FSGD2104E FPGA

| 系统逻辑单元 (K) | 2,586 |

|---|---|

| DSP Slice | 6,840 |

| 内存 (Mb) | 345.9 |

| GTY 32.75Gb/s 收发器 | 76 |

| I/O | 676 |

产品信息

开发板特性

包含VCU1525 开发板

存储器

- 4 - 16GB DDR4 DIMM

功耗与热量

- 被动散热(用户必须确保在散热器间有气流)

- 225W 最大动态电源

- PCIe 边缘接插件的最大功率达 75W

- 从 PCIe 辅助电源接插件提高额外 150W 功率

配置

- 通过 JTAG thru Micro USB 端口进行 FPGA 配置

- QSPI 配置 flash 存储器

通信与网络

- 两个 QSFP28 100G 接口

- 通过板边接插件支持 PCIe Gen3 x 16 或 Gen4 x8

内含物件

支持 XCVU9P-L2FSGD2104E 的 VCU1525 开发板

Vivado™ Design Suite: Design Edition 凭证代码

XCVU9P FPGA 节点锁定与设备锁定,更新期为 1 年

USB Micro 电缆

资源

设计工具

| 名称 | 描述 | 许可证类型 |

|---|---|---|

| Vivado Design Suite Design Edition | AMD Vivado™ Design Suite 是一款以 IP 核及系统为中心的设计环境,这一全新构建的环境具有革新意义,能够显著加速 FPGA 和 SoC 系列器件的设计效率。 | XCVU9P FPGA 节点锁定与器件锁定,更新期为 1 年。 支持部分重配置 |

| SDAccel 开发环境 | SDAccel 是 OpenCL 应用的开发环境,主要面向基于 PCIe® 的 AMD FPGA 加速卡。该环境支持系统处理器和 FPGA 逻辑的同步编程,无需 RTL 设计经验。 | XCVU9P FPGA 节点锁定与器件锁定,更新期为 1 年。 |

| Dynamic Function eXchange | Dynamic Function eXchange 可通过下载部分比特文件动态修改逻辑块,而其余逻辑将继续不间断运行。AMD Dynamic Function eXchange 技术助力设计人员实时改变加速器电路板的功能性,重新加载时无需全面重新配置,也无需重新构建 PCIe 链路。 | XCVU9P FPGA 节点锁定与器件锁定,更新期为 1 年。 |

IP 核

| 名称 | 描述 | 许可证类型 |

|---|---|---|

| DDR4 SDRAM Controller | DDR4 SDRAM 控制器是 Vivado IP Catalog 中的免费 IP core。 | 免费 IP |

| DMA for PCI Express (PCIe) Subsystem | 面向 PCI Express (PCIe) 的 AMD LogiCORE™ DMA 可实现高性能、可配置的分散集中 DMA,支持对 PCI Express 3.x 集成型模块的使用。 该 IP 提供 AXI4 或 AXI4-Stream 可选用户接口。 | 免费 IP |

| AMD SmartConnect 技术 | 通过解决高性能数百万系统逻辑单元设计中的系统互联瓶颈问题, AMD SmartConnect 技术能为 UltraScale+™ 产品组合带来前所未有的高性能。 | 免费 IP |

| 面向定制开发板支持的 SDAccel 平台参考设计 | SDAccel 项目可针对目标平台进行编译。SDAccel 平台参考设计是开发板和软硬件架构组件的完美结合,可通过它执行 OpenCL 应用内核。 该参考设计可帮助平台开发者为其定制 PCIe 开发板添加 DAccel 支持。 | 免费 IP |

设置 VCU1525 加速器卡

2018.3

下载 Xilinx 运行时和部署 Shell。

1.

下载 Xilinx 运行时

Xilinx 运行时 (XRT) 是主机和板卡之间的低层次通信层(API 和驱动)。

重要提示:请在安装 XRT 之前输入以下命令:

RedHat:

$ sudo yum-config-manager --enable rhel-7-server-optional-rpms

$ sudo yum install -y https://dl.fedoraproject.org/pub/epel/epel-release-latest-7.noarch.rpm

社区企业操作系统:

$ sudo yum install epel-release

2.

下载部署 Shell

部署 shell 是物理实现并闪存到卡中的通信层。

注意:

VCU1525 将利用这个 shell 进行应用开发(卡本身仅用于开发,且不适合作为终端系统的一部分进行卷部署)。

开发自己的 VCU1525 加速应用

如果您是开发者,请下载这些文件。

3.

下载开发 Shell

如果要构建自己的应用,则需要用于开发的 shell 接口。

4.

下载 SDAccel 设计环境

AMD SDAccel IDE 为开发加速应用提供了框架。