基于 FPGA 的原型设计

在 ASIC 或 SoC 可用之前,

实现早期软件集成和固件开发

概述

基于 FPGA 的原型设计是在一个包含一个或多个 FPGA 的平台上实现/综合 ASIC RTL 的过程。原型设计在流片之前完成,作为芯片前系统验证流程的一部分,但也可用于软件开发的后期流片。此外,原型设计平台还包括与目标 ASIC 一起使用的外设及内存的接口。

硬件验证和 SW/FW 开发是 SoC 设计成本的主导因素。在流片之前,原型设计过程中的软硬件协同验证允许开发人员在真实部件供货之前,启动软件,实现自定义特性。此外,使用 AMD Vivado™ Design Suite,还可协同优化设计流程,其不仅可降低成本和流片风险,而且还可提高效率,缩短上市时间。

对于基于 FPGA 的原型设计,AMD 解决方案:

- 可提供高性能 FPGA,加速目标设计的验证

- 减少了板级空间的要求和复杂性

- 实现灵活 I/O,创建邻接器件

- 实现高级调试、仿真加速和交互式设计微调

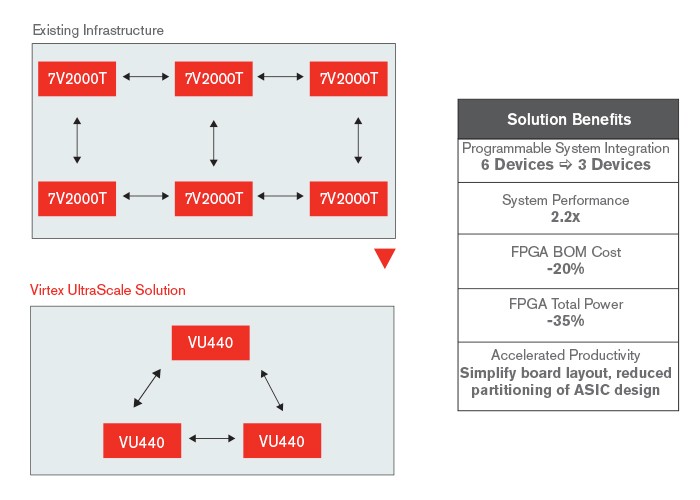

凭借 Virtex™ 7 2000T FPGA 和 Virtex UltraScale™ VU440 FPGA,AMD 一直是最大容量 FPGA 的市场领导者。16nm Virtex UltraScale+™ 系列现在包括世界上容量最大的 FPGA - Virtex UltraScale+ VU19P FPGA,实现高端器件连续三代的持续领先。

Virtex 7 2000T

构建时,充分考虑到了 SoC 原型设计

- 2M 逻辑单元、 6.8B 晶体管

- 36 个 12.5Gb/s 串行收发器

- 46 Mb block RAM

- 1,200 个 I/O

- 第一代 SSI 技术

Virtex UltraScale VU440

在 20nm 下将器件密度提高 4 倍

- 5.5M 系统逻辑单元、 20B 晶体管

- 48 个 16.3Gb/s 串行收发器

- 89 Mb block RAM

- 1,456 个 I/O

- 第二代 SSI 技术

Virtex UltraScale+ VU19P

具全球最大容量的 FPGA

- 拥有 900 万个系统逻辑单元、35B 晶体管

- 80 个 28Gb/s 串行收发器

- 94.5Mb block RAM

- 2,072 个 I/O

- 第三代 SSI 技术

技术文档

设计范例

使用 AMD UltraScale™ 架构,ASIC 原型 & 仿真可实现突破性性能和集成。 Virtex™ UltraScale 器件通过高逻辑容量、超过 90% 器件利用率、堪比 ASIC 的时钟、增强型布线和面向引脚多路复用的高速收发器简化设计分区。突破性架构融合 Vivado™ Design Suite 为满足领先的 ASIC 和 SoC 平台需求提供了理想的解决方案。

解决方案概述与优势

- 突破性器件容量 降低分区数量,并简化开发板布局

- Vivado Design Suite 增强型布线和协同优化确保超过 90% 的器件利用率

- 堪比 ASIC 的时钟性能 有效地映射复杂的 ASIC 和 SoC 时钟树

- 高速收发器 实现 FPGA 之间高效的引脚多路复用,并支持下一代系统的 I/O 接口需求

UltraScale 架构优势

- 海量 I/O 带宽

- 提供超过 1 Tbps 的芯片对芯片带宽

- 低延时收发器实现芯片间互连

- 海量数据流 & 路由

- 支持高性能的本地 ASIC 总线

- 支持高性能的本地 ASIC 总线

- 堪比 ASIC 的时钟性能

- 最大化复杂 SoC 原型设计的灵活性

- 最大化复杂 SoC 原型设计的灵活性

- 系统性能

- 单器件性能提升 15-30 %

- 分区减少,性能提升 3 倍

- 功耗管理

- 系统功耗最多可降低 35%