- 应用

- 测试 & 测量解决方案

- 半导体自动测试设备

新一代 SoC 测试器需要测试更广泛的 IO 协议,其复杂性和速度都在不断提升。行业领先的 SerDes 和 HSSIO 技术能够以最佳的成本提供最高的灵活性,从而可实现高容量 SoC 测试器与存储器测试器。存储控制器的集成硬 IP 以及芯片对芯片互联可减少资源使用,以实现符合成本效益的解决方案。

| 设计范例 | 说明 | 器件支持 |

|---|---|---|

点击放大 |

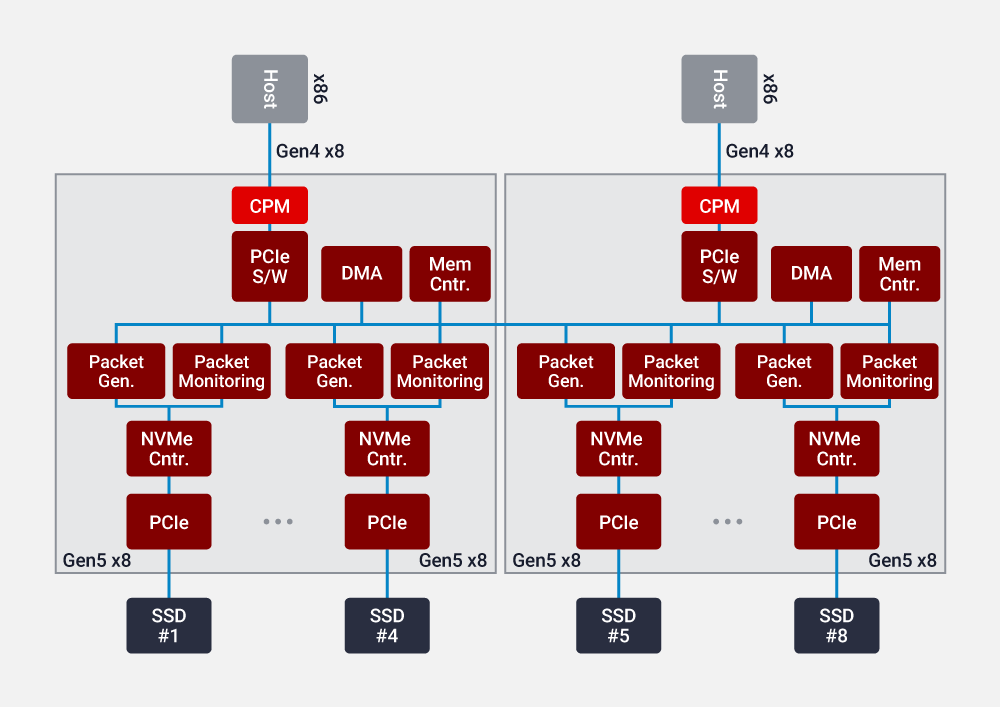

SoC 和存储测试器 创新的 Versal™ 架构为系统设计人员提供了任何其它器件解决方案都无法提供的性能、灵活性和功耗优化硬 IP。Versal Premium 自适应 SoC 中的 AI 引擎和 DSP 引擎可提供无与伦比的信号处理功能,具有更快的片上/片外内存带宽。灵活应变引擎中的 7.5M 系统逻辑单元可为定制 IP、流量生成和监控功能性提供高度的灵活性,将在开发 ATE 的过程中发挥重要作用。可扩展的 112G PAM4 收发器和功耗优化的硬 IP,如 600G 以太网 MAC、400G 高速加密引擎、DDR 内存控制器和集成型 PCIe® Gen5 模块等,都是预先设计的,可通过各种不同的特性和性能选项支持最流行的接口标准。 |

Versal Premium 自适应 SoC |

点击放大 |

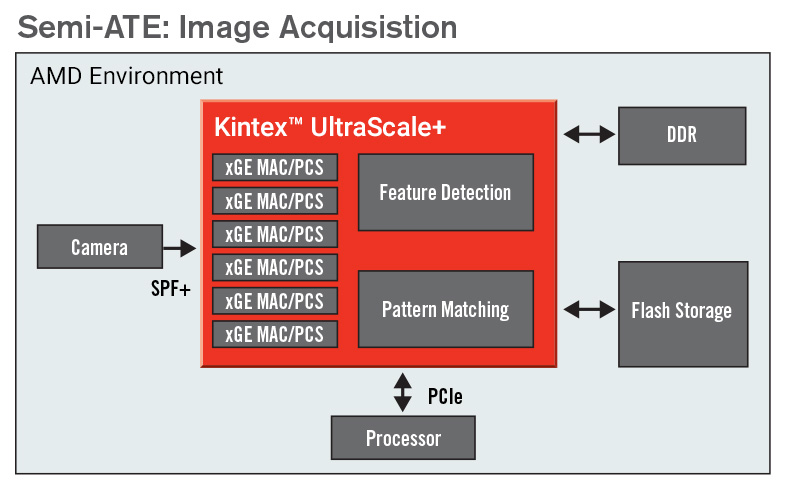

半导体 ATE:图像采集 图像采集需要高性能收发器和 DSP 功能,同时还需要为低成本应用保持低功耗以及器件低成本。Kintex™ UltraScale+™ 可实现单位功耗性价比的最佳平衡,可为各种高级功能提供最低成本的解决方案,这些功能包括 32Gbps 收发器、6.3 TeraMAC 的 DSP 计算性能、2.6Gbs DDR4 以及 PCIe Gen4x8 支持等。 |

|

点击放大 |

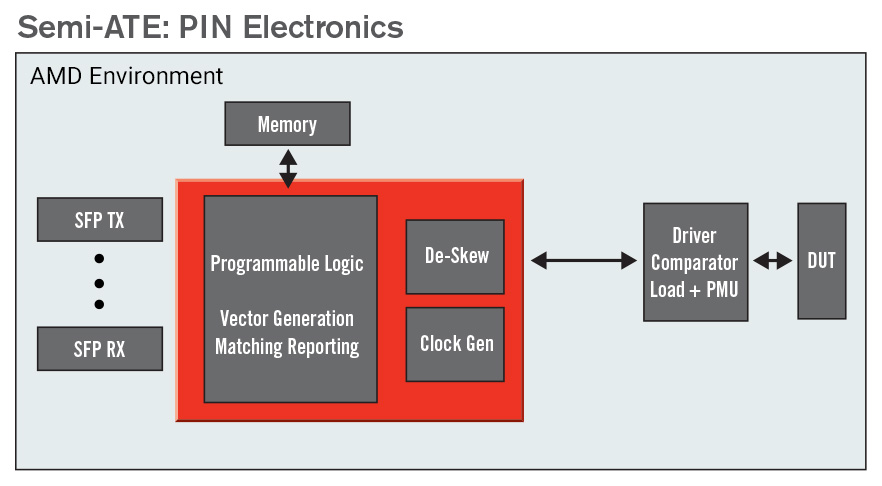

半导体 ATE:PIN 电子产品 PIN 电子产品可为矢量生成与分析以及大量高性能 IO 调用低成本 FPGA,以便使用并行接口连接大量的 ASSP。鉴于 1Gbps+ 的链路速度、不利的通道以及较少的参考时钟,IO 缓冲与时钟生成/分配功能必须非常高级,才能管理多通道间的歪斜以及过私密信件。Kintex UltraScale+ FPGA 具有高性能,采用功能丰富的 SelectIO™ 收发器,从而可提供信号调节功能、基于 PLL 及 DLL 的时钟生成与分配资源,以及歪斜管理功能。因此,Kintex UltraScale+ FPGA 是 PIN 电子产品应用的理想选择。 |